http://www.synopsys.com.cn/information/snug/2009/low-power-implementation-flow-based-ieee1801-upf

2.1 Synopsys基于UPF的低功耗设计流程

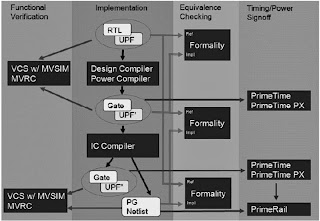

Synopsys公司提供了完整的基于UPF的低功耗综合、物理实现和验证流程,如图7所示。该流程始于寄存器传输级(RTL)描述的逻辑设计,加上一个独立的描述低功耗设计意图的UPF文件。RTL和UPF描述分别放在独立的文件中,使他们可以单独维护和修改。在这个示例中,最初的UPF文件标志为UPF。

Design Compiler读入RTL和初始UPF描述文件,基于它们综合出门级网表并产生一个更新了的UPF文件,这个Design Compiler输出的UPF文件在示例图中标志为UPF’。UPF’文件中包含了原始UPF文件的内容,并添加了综合时加入的对某些特殊cell(比如isolation cells、level shifters)的电源和地的连接关系。综合输出的门级网表已经被工具根据UPF的相应描述插入了一些低功耗所需的特殊电路单元,比如Level-Shifter,Isolation cells,Retention Register等。

IC Compiler读入综合输出的门级网表和UPF’描述文件,基于它们进行物理实现,包括:布局和布线以及电源关断特殊单元(Power-Gating cell)的插入、摆放和控制信号线的连接等步骤。输出一个新的门级网表,一个包括所有cell的电源和地连接关系的网表(俗称pg网表),以及一个更新了的UPF文件,标志为UPF’’。UPF’’文件包含了UPF’的内容,并添加了在物理实现阶段对低功耗电路结构的改变,比如添加了Power Switches(俗称MTCMOS)的连接关系。

这个flow中产生的数据可以用于做功能仿真(利用MVSIM、VCS),插入的低功耗单元的正确性检查(利用MVRC),形式验证(利用Formality),以及时序功耗检查(利用Prime Time-PX)和电压降(IR-Drop)(利用Prime Rail)的验证。

VCS仿真器和MVSIM多电压仿真工具可以在几个阶段用来做多电压的功能仿真:RTL级,综合后加入了低功耗相关器件(比如Isolation cell)的门级,以及PR之后加入了Power Switches的门级。MVRC用于检查多电压设计的规则是否正确实现,包括电源连接关系、电源结构、电源一致性等等,也适用于流程中的各个步骤。

Prime Time读入DC或ICC输出的门级网表以及对应的UPF文件。它利用UPF文件中的信息建立一个虚拟的电源网络模型,并将电压值反标到每个器件的电源端口,进行带电源信息的时序检查。

Prime Rail是基于带UPF信息的版图进行电压降以及电迁移的分析。如果设计中有电源关断单元,它还可以分析相关关断电路的瞬态电流以及动态的电压降分布。来帮助判断这些电源关断单元是否插入合理以及是否需要插入De-cap单元。

2.2 UPF所需要的特殊单元库

基于UPF的设计流程与传统流程相比,需要一些库中特殊单元的支持以及对传统的DB时序库添加电源地的信息。特殊单元包括Level-shifter,Isolation Cell,电源关断单元(Power Gating, 也叫MTCMOS),Retention-Register,以及Always-on单元。下面分别阐述:

没有评论:

发表评论